|

| Transistor MOSFET em 2D. |

Existem três partes:

Source (Fonte) – Por onde entra a corrente elétrica, corrente essa que será ligada ou desligada.

Gate (Porta) – Onde entra a tensão que controla o fluxo ou corte de corrente elétrica.

Drain (Dreno) – Por onde sai a corrente elétrica que veio de Source, quando a corrente não é cortada pela tensão de Gate.

Além disso, os transistores MOSFET possuem uma camada isolante de dióxido de silício (SIO2), que isola as portas do transistor do canal de condução de corrente elétrica, e de substratos de silício tipo P e silício tipo N. Se o canal for feito de silício tipo N e o substrato de silício tipo P trata-se de um transistor tipo N (NMOSFET), se for ao contrário trata-se de um transistor tipo P (PMOSFET). Veja abaixo: |

| Estrutura de um E-MOSFET de canal N. |

MOSFET tipo Depleção:

Quando há uma tensão de porta negativa a tensão VDD força os elétrons que estão livres a fluírem da fonte para o dreno. A tensão da porta controla a largura do canal de corrente elétrica. Quanto mais negativa a tensão menor a largura do canal e conseqüentemente menos corrente elétrica passa da fonte para o dreno. Se a tensão negativa porta-fonte (Vgs) exceder um limite o canal é fechado e a corrente elétrica é cortada. A operação do MOSFET no modo Depleção se dá quando Vgs está entre Vgs-off (canal fechado) e 0 volt (canal conduzindo corrente elétrica). Abaixo símbolo e esquema do MOSFET tipo Depleção (D-MOSFET): |

| Símbolo de um D-MOSFET. |

|

| Esquema de um D-MOSFET. |

MOSFET tipo Intensificação:

Nos transistores MOSFET tipo intensificação (E-MOSFET) o substrato se estende até o dióxido de silício. Essa é a diferença para os D-MOSFET. Veja abaixo o esquema e o símbolo dos E-MOSFET: |

| Símbolo e Esquema de um E-MOSFET. |

O E-MOSFET possui uma tensão positiva mínima para a criação de um canal de corrente elétrica entre o substrato e o dióxido de silício, permitindo o fluxo de elétrons livres entre a fonte e o dreno (corrente de dreno). Essa tensão é chamada de tensão limiar.

Acima de um limite de tensão negativa ou positiva o transistor é danificado, pois a camada isolante de dióxido de silício, que é muito fina, é destruída pela tensão muito alta.

Veja abaixo a curva de dreno dos E-MOSFET: |

| Curva de dreno dos E-MOSFET. |

Enquanto Vgs (tensão porta-fonte) não atinge Vgs (th) (tensão limiar), não há corrente de dreno. Há um limite de saturação para Vgs, a partir do qual a corrente de dreno não aumenta mais.

Os gráficos abaixo resumem o funcionamento dos D-MOSFET e E-MOSFET: |

| Resumo de funcionamento dos D-MOSFET e E-MOSFET. |

Portanto podemos construir circuitos lógicos eletrônicos (processadores) utilizando transistores tipo P (D-MOSFET e E-MOSFET) ou N (D-MOSFET e E-MOSFET). Por exemplo, podemos construir três tipos de porta Not (Inversora) com os transistores MOSFET:

|

| Porta NOT tipo NMOS. |

|

| Porta NOT tipo PMOS. |

|

| Porta NOT tipo CMOS. |

Há o Resistor-Transistor Logic (RTL) e o Transistor-Transistor Logic (TTL).

Lembrando que a porta Not inverte o sinal de entrada: se for 1 sai 0; se for 0 sai 1.

Vamos entender o funcionamento:

A terceira porta Not (tipo TTL) tem dois transistores, uma entrada A, uma saída Q, uma tensão VSS e uma tensão VDD. Adotaremos como exemplo VSS = 0 volt (significando 0) e VDD = 5 volts (significando 1). Se precisar revise o sistema binário dos computadores. O transistor MOSFET com a bolinha opera em modo de Depleção e o transistor MOSFET sem bolinha opera em modo de Intensificação.

Se a entrada for igual a 0 volt a saída é igual a 5 volts; isso porque 0 volt faz com que o D-MOSFET (o da bolinha) conduza corrente elétrica (5 volts) de VDD até a saída Q, e o E-MOSFET (sem bolinha), por sua vez, quando recebe 0 volt não conduz 0 volt (terra) até a saída Q.

Se a entrada for igual a 5 volts a saída é igual a 0 volt; isso porque 5 volts fazem com que o D-MOSFET (o da bolinha) não conduza corrente elétrica (5 volts) de VDD até a saída Q, e o E-MOSFET (sem bolinha), por sua vez, quando recebe 5 volts conduz 0 volt (terra) até a saída Q.

As outras duas portas Not das figuras (tipo RTL) funcionam de maneira semelhante, mas possuem um resistor para funcionarem com apenas um transistor. A porta Not com dois transistores tem melhor desempenho, pois gasta menos energia e tem maior velocidade de processamento.

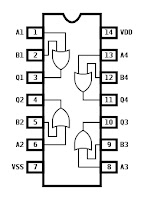

Veja abaixo o símbolo de uma porta lógica Not e o esquema de um pequeno chip com portas Not: |

| Símbolo da porta NOT (Inversora). |

Segundo exemplo: podemos construir uma porta lógica do tipo OR com transistores MOSFET, tipo N ou tipo P, arranjados na forma CMOS. Veja a figura:

|

| Porta OR tipo CMOS. |

A porta lógica OR (OU) tem duas entradas A e B, uma saída Q, uma tensão VSS e uma tensão VDD. Como exemplo vamos utilizar VSS = 0 volt (significando 0) e VDD = 5 volts (significando 1).

Vejamos qual sinal (0 ou 1) deve ser obtido na saída Q, dependendo de quais sinais estão entrando nas entradas A e B:

ENTRADA

|

SAÍDA

| |

A

|

B

|

Q

|

0

|

0

|

0

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

Portanto a saída Q só é igual a 0 se ambas as entradas A e B forem iguais a zero.

Vamos entender o funcionamento:

Os transistores 3, 4 e 6 operam em modo Intensificação.

Os transistores 1, 2 e 5 operam em modo Depleção.

Se A = 0 e B = 0 então:

Os transistores 1 e 2 (Depleção) conduzem corrente elétrica de VDD (5 volts) até as portas dos transistores 5 e 6. Os transistores 3 e 4 (Intensificação) não conduzem corrente elétrica de VSS (0 volt) até as portas dos transistores 5 e 6. Portanto a tensão VDD (5 volts) chega nas portas dos transistores 5 e 6. O transistor 5 (Depleção) não conduz corrente elétrica de VDD (5 volts) para a saída Q. E em fim o transistor 6 (Intensificação) conduz a tensão VSS (0 volt) até a saída Q. Portanto se A = 0 e B = 0 => Q = 0.

Se A = 0 e B = 1 então:

O transistor 1 (Depleção) conduz corrente elétrica de VDD (5 volts), mas o transistor 2 (Depleção) recebe o sinal 1 da entrada B e não conduz corrente elétrica. Portanto, os transistores 1 e 2 não conduzem corrente elétrica de VDD (5 volts) até as portas dos transistores 5 e 6. O transistor 3 também não conduz corrente. Porém o transistor 4 (Intensificação) que recebe o sinal 1 da entrada B conduz a tensão VSS (0 volt) até as portas dos transistores 5 e 6. O transistor 5 (Depleção) quando recebe VSS (0 volt) conduz corrente elétrica de VDD (5 volts) até a saída Q. O transistor 6 (Intensificação) quando recebe a tensão VSS (0 volt) não conduz VSS (0 volt) até a saída Q. Portanto se A = 0 e B = 1 => Q = 1.

Se A = 1 e B = 0 então:

O transistor 2 (Depleção) está apto a conduzir corrente elétrica, mas o transistor 1 (Depleção) não conduz corrente porque está recebendo o sinal 1 da entrada A. Com isso os transistores 1 e 2 não conduzem corrente elétrica de VDD (5 volts) até as portas dos transistores 5 e 6. O transistor 4 (Intensificação) não conduz corrente, mas o transistor 3 (Intensificação) que recebe o sinal 1 da entrada A conduz corrente 0A de VSS (0 volt) até as portas dos transistores 5 e 6. Com isso o transistor 5 (Depleção) conduz corrente elétrica de VDD (5 volts) para a saída Q. Por último o transistor 6 (Intensificação) não conduz VSS (0 volt) para a saída Q. Portanto se A = 1 e B = 0 => Q = 1.

Se A = 1 e B = 1 então:

Os transistores 1 e 2 (Depleção) não conduzem a tensão VDD (5 volts) até as portas dos transistores 5 e 6, porém os transistores 3 e 4 (Intensificação) conduzem VSS (0 volt) até as portas dos transistores 5 e 6. Com isso o transistor 5 (Depleção) conduz corrente elétrica de VDD (5 volts) para a saída Q. O transistor 6 (Intensificação) não conduz VSS (0 volt) para a saída Q. Portanto se A = 1 e B = 1 => Q = 1.

Veja abaixo o esquema de um pequeno circuito que utiliza portas lógicas Or.

As portas lógicas descritas acima implementam as funções booleanas NOT e OR. Existem outras diversas funções booleanas como por exemplo AND, NAND, NOR, XOR, XNOR etc. Existem portas lógicas que implementam todas as funções booleanas, uma porta para cada função, e com isso nós podemos combiná-las para fazer circuitos complexos como somadores, subtratores, multiplicadores, divisores, memórias com flip-flops, controladores de memória, micro-controladores, comparadores, deslocadores à esquerda e à direita, contadores, incrementador, decrementador, unidades que executam instruções etc. Em fim, podemos construir processadores super complexos inteiros com milhões de portas lógicas super integradas em escala muito pequena em uma placa de silício de 1 cm².